# PAN4620

IEEE® 802.15.4 and Bluetooth® Low Energy Module

# **Product Specification**

Rev. 0.1

The PAN4620 is Panasonic's Internet of Things dual mode module comprising NXP<sup>®</sup>'s Kinetis MKW41Z512CAT4 SoC - a 2.4 GHz 802.15.4 and Bluetooth<sup>®</sup> Low Energy wireless radio microcontroller based on an ARM<sup>®</sup> Cortex-M0+ core.

#### **Features**

- UART, SPI, I2C, TSI, ADC & DAC

- Same form factor and compatible pinout for VCC, GND, Reset, UART, I<sup>2</sup>C, and SWD as PAN1026, PAN1760, PAN1760A, and PAN1761

- Single and concurrent operation of IEEE<sup>®</sup> 802.15.4 and BLE

- Open to various known application layers or proprietary solutions

- Surface Mount Type dimensions: 15.6 mm x 8.7 mm x 1.9 mm

- On module 32 MHz and 32 kHz crystal

- SoC: NXP<sup>®</sup> Kinetis<sup>®</sup> KW41Z 2.4 GHz 802.15.4 and BLE 4.2 Wireless Radio Microcontroller

- Core: Up to 48 MHz 32 bit ARM® Cortex-M0+

- Memory: 512 kB of flash and 128 kB of SRAM

- Voltage range: 1.8 V to 4.2 V

- Temperature range: -40 °C to 85 °C

#### **Characteristics**

- Transceiver frequency range 2360 MHz to 2483.5 MHz

- Programmable transmitter output power:

-30 dBm to 3 dBm

- Receiver sensitivity (BLE): -93 dBm

- Receiver sensitivity typical for IEEE<sup>®</sup> Standard 802.15.4: -98 dBm

- Typical receiver current consumption (3.6 V supply): 8.5 mA

- Transmitter current consumption (3.6 V supply, 0 dBm): 7.6 mA

#### Bluetooth®

- Bluetooth<sup>®</sup> LE 4.2 compliant implementation certified by BT SIG

- Supporting software consisting of BLE host stack and profiles and IPv6 6LoBLE

- Bluetooth<sup>®</sup> Developer Studio Plug-In

### IEEE<sup>®</sup> 802.15.4

- IEEE<sup>®</sup> standard 802.15.4 compliant

- Supporting software consisting of 802.15.4 MAC/PHY implementation, Simple Media Access Controller (SMAC), and NXP<sup>®</sup>'s certified Thread<sup>®</sup> stack

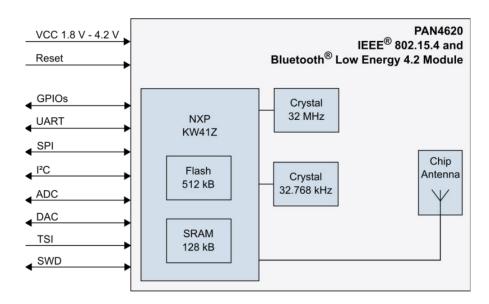

### **Block Diagram**

By purchase of any of the products described in this document the customer accepts the document's validity and declares their agreement and understanding of its contents and recommendations. Panasonic Industrial Devices Europe GmbH (Panasonic) reserves the right to make changes as required at any time without notification. Please consult the most recently issued Product Specification before initiating or completing a design.

© Panasonic Industrial Devices Europe GmbH 2017.

This specification sheet is copyrighted. Reproduction of this document is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Do not disclose it to a third party.

All rights reserved.

This Product Specification does not lodge the claim to be complete and free of mistakes.

#### **Engineering Samples (ES)**

If Engineering Samples are delivered to the customer, these samples have the status "Engineering Samples". This means that the design of this product is not yet concluded. Engineering Samples may be partially or fully functional, and they may differ from the published Product Specification.

Engineering Samples are not qualified and they are not to be used for reliability testing or series production.

#### Disclaimer

The customer acknowledges that samples may deviate from the Product Specification and may bear defects due to their status of development and the lack of qualification mentioned above.

Panasonic rejects any liability or product warranty for Engineering Samples. In particular, Panasonic disclaims liability for damages caused by:

- The use of the Engineering Sample other than for evaluation purposes, particularly the installation or integration in another product to be sold by the customer,

- Deviation or lapse in function of the Engineering Sample,

- Improper use of the Engineering Sample.

Panasonic Industrial Devices Europe GmbH disclaims any liability for consequential and incidental damages. In case of any queries regarding the Engineering Samples, please contact your local sales partner or the related product manager.

# **Table of Contents**

| 1 | Abou  | t This Document                                                 | 6  |

|---|-------|-----------------------------------------------------------------|----|

|   | 1.1   | Purpose and Audience                                            | 6  |

|   | 1.2   | Revision History                                                | 6  |

|   | 1.3   | Use of Symbols                                                  | 6  |

|   | 1.4   | Related Documents                                               | 6  |

| 2 | Overv | view                                                            | 7  |

|   | 2.1   | Block Diagram                                                   | 8  |

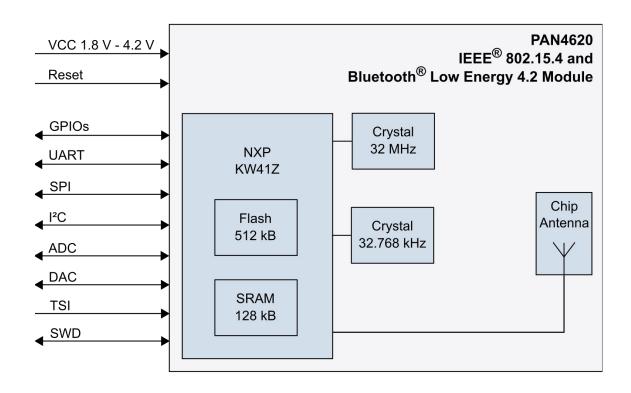

|   | 2.2   | Pin Configuration                                               | 9  |

|   | 2.3   | Transceiver Features                                            | 13 |

| 3 | Detai | led Description                                                 | 16 |

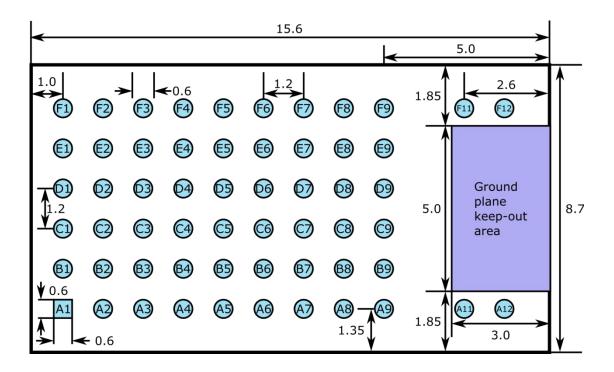

|   | 3.1   | Dimensions                                                      | 16 |

|   | 3.2   | Footprint                                                       | 17 |

|   | 3.3   | Packaging                                                       | 18 |

|   | 3.4   | Case Marking                                                    | 21 |

| 4 | Spec  | ification                                                       | 22 |

|   | 4.1   | Default Test Conditions                                         |    |

|   | 4.2   | Absolute Maximum Ratings                                        |    |

|   | 4.3   | Recommended Operating Conditions                                |    |

|   | 4.4   | Current Consumption                                             |    |

|   | 4.5   | Internal Operating Frequencies                                  |    |

|   | 4.6   | Interface Specification                                         | 25 |

|   | 4.7   | Flash electrical specifications                                 | 40 |

|   | 4.8   | General switching specification                                 | 41 |

|   | 4.9   | Transceiver Feature Summary                                     | 42 |

|   | 4.10  | Reliability Tests                                               | 47 |

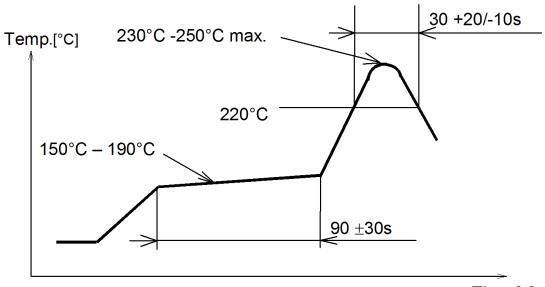

|   | 4.11  | Recommended Soldering Profile                                   | 48 |

| 5 | Cauti | ons                                                             | 49 |

|   | 5.1   | Design Notes                                                    | 49 |

|   | 5.2   | Installation Notes                                              | 49 |

|   | 5.3   | Usage Condition Notes                                           | 50 |

|   | 5.4   | Storage Notes                                                   | 50 |

|   | 5.5   | Safety Cautions                                                 | 50 |

|   | 5.6   | Other Cautions                                                  | 51 |

|   | 5.7   | Life Support Policy                                             | 51 |

| 6 | Regu  | latory and Certification Information                            | 52 |

|   | 6.1   | Federal Communications Commission (FCC) for US                  | 52 |

|   | 6.2   | Innovation, Science, and Economic Development (ISED) for Canada | 52 |

|   | 6.3   | European Conformity According to RED (2014/53/EU)               |    |

|   | 6.4   | Bluetooth <sup>®</sup>                                          | 52 |

|   | 6.5   | RoHS and REACH Declaration                                      | 52 |

| 7 | Appe  | ndix                                                            | 53 |

|   | 7.1   | Ordering Information                                            | 53 |

| - |       |                                                                 |    |

| 7.2 | List of Acronyms | .54 |

|-----|------------------|-----|

| 7.3 | Contact Details  | 55  |

1 About This Document

### 1 About This Document

### 1.1 Purpose and Audience

This Product Specification provides details on the functional, operational, and electrical characteristics of the Panasonic PAN4620 module. It is intended for hardware design, application, and Original Equipment Manufacturers (OEM) engineers. The product is referred to as "the PAN4620" or "the module" within this document.

### 1.2 Revision History

| Revision | Date       | Modifications/Remarks    |

|----------|------------|--------------------------|

| 0.1      | 28.02.2018 | 1st preliminary version. |

### 1.3 Use of Symbols

| Symbol                             | Description                                                                                                                                      |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| (1)                                | Note Indicates important information for the proper use of the product. Non-observance can lead to errors.                                       |

| $\triangle$                        | Attention Indicates important notes that, if not observed, can put the product's functionality at risk.                                          |

| ⇒ [chapter number] [chapter title] | Cross reference Indicates cross references within the document.  Example:  Description of the symbols used in this document   1.3 Use of Symbol. |

#### 1.4 Related Documents

Please refer to the Panasonic website for related documents ⇒ 7.3.2 Product Information.

#### 2 Overview

The PAN4620 is Panasonic's Internet of Things dual mode module comprising NXP's Kinetis KW41Z SoC - a 2.4 GHz 802.15.4 and Bluetooth® Low Energy wireless radio microcontroller based on an ARM® Cortex-M0+ core.

To provide maximum flexibility, the module can be operated in stand-alone and hosted mode. With 512 kB flash memory and 128 kB SRAM the PAN4620 can easily be used as a stand-alone controller eliminating the need for an external processor, saving complexity, space and cost. It is thus well suited for very small and low-power applications. However, also the integration of 802.15.4 and/or BLE connectivity into existing applications can easily be achieved when using the PAN4620 in hosted mode.

Using the PAN4620 with low power consumption in combination with NXP<sup>®</sup>'s certified Thread<sup>®</sup> stack, BLE stack or a combination of both for concurrent operation allows to meet IoT application requirements without the need for a gateway. Since Thread<sup>®</sup> does not define an application layer, various application layers can be used, such as dotdot, IoTivity, OpenDOF, and others.

FCC, IC, and CE approval are under way.

Please refer to the Panasonic website for related documents ⇒ 7.3.2 Product Information.

Further information on the variants and versions ⇒ 7.1 Ordering Information.

For further information please also refer to the MKW41Z512CAT4 <u>datasheet</u> and <u>reference</u> <u>manual</u> from NXP<sup>®</sup>.

### 2.1 Block Diagram

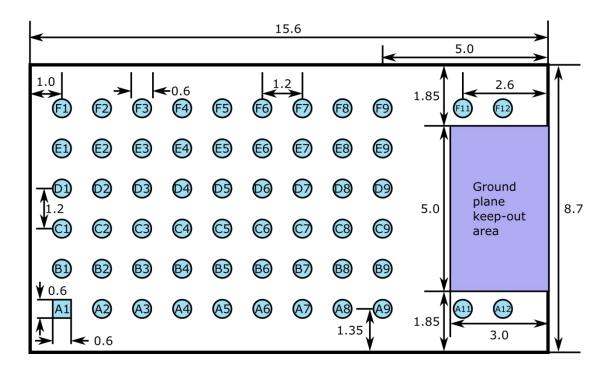

### 2.2 Pin Configuration

#### **Pin Assignment**

#### Top view with all values in [mm]

**Pin Functions**

| No | Pin Name | Alternative Pin                                                              | Pin Type    | Description                                                       |

|----|----------|------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------|

| A1 | GND      |                                                                              | Ground      | Connect to ground                                                 |

| A2 | NC       |                                                                              |             | Not connected                                                     |

| A3 | RESET    | PTA2, TPM0_CH3                                                               | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| A4 | NC       |                                                                              |             | Not connected                                                     |

| A5 | VCC      |                                                                              | Power       | Supply voltage 1.8 V to 4.2 V                                     |

| A6 | VCC      |                                                                              | Power       | Supply voltage 1.8 V to 4.2 V                                     |

| A7 | GND      |                                                                              | Ground      | Connect to ground                                                 |

| A8 | PTC18    | TSI0_CH6, LLWU_P2,<br>SPI0_SIN, I2C1_SDA,<br>LPUART0_TX,<br>BSM_DATA, DTM_TX | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| No  | Pin Name | Alternative Pin                                                               | Pin Type    | Description                                                       |

|-----|----------|-------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------|

| A9  | GND      |                                                                               | Ground      | Connect to ground                                                 |

| A11 | GND      |                                                                               | Ground      | Connect to ground                                                 |

| A12 | GND      |                                                                               | Ground      | Connect to ground                                                 |

| B1  | NC       |                                                                               |             | Not connected                                                     |

| B2  | PTA17    | TSI0_CH11, LLWU_P5,<br>RF_RESET, SPI1_SIN,<br>TPM_CLKIN1                      | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| В3  | PTC19    | TSI0_CH7, LLWU_P3, SPI0_PCS0, I2C0_SCL, LPUART0_CTS_b, BSM_CLK, BLE_RF_ACTIVE | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| B4  | PTC17    | TSI0_CH5, LLWU_P1 SPI0_SOUT, I2C1_SCL LPUART0_RX, BSM_FRAME, DTM_RX           | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| B5  | PTC16    | TSI0_CH4, LLWU_P0,<br>SPI0_SCK, I2C0_SDA,<br>LPUART0_RTS_b,<br>TPM0_CH3       | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| В6  | PTA16    | TSI0_CH10, LLWU_P4,<br>SPI1_SOUT, TPM0_CH0                                    | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| В7  | NC       |                                                                               |             | Not connected                                                     |

| В8  | NC       |                                                                               |             | Not connected                                                     |

| В9  | NC       |                                                                               |             | Not connected                                                     |

| C1  | NC       |                                                                               |             | Not connected                                                     |

| C2  | PTA19    | TSI0_CH13, ADC0_SE5,<br>LLWU_P7, SPI1_PCS0,<br>TPM2_CH1                       | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| С3  | PTA18    | TSI0_CH12, LLWU_P6,<br>SPI1_SCK, TPM2_CH0                                     | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| C4  | SWDIO    | PTA0, TSI0_CH8,<br>SPI0_PCS1, TPM1_CH0,<br>SWD_DIO                            | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| C5  | SWDCLK   | PTA1, TSI0_CH9,<br>SPI1_PCS0, TPM1_CH1,<br>SWD_CLK                            | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| No | Pin Name | Alternative Pin                                                                 | Pin Type    | Description                                                       |

|----|----------|---------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------|

| C6 | PTC1     | I2CO_SDA, LPUARTO_RTS_b, TPMO_CH2, BLE_RF_ACTIVE                                | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| C7 | NC       |                                                                                 |             | Not connected                                                     |

| C8 | GND      |                                                                                 | Ground      | Connect to ground                                                 |

| C9 | GND      |                                                                                 | Ground      | Connect to ground                                                 |

| D1 | РТВ0     | LLWU_P8,<br>XTAL_OUT_EN,<br>I2C0_SCL, CMP0_OUT,<br>TPM0_CH1, CLKOUT             | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| D2 | PTB1     | ADC0_SE1, CMP0_IN5,<br>DTM_RX, I2C0_SDA,<br>LPTMR0_ALT1,<br>TPM0_CH2, CMT_IRO   | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| D3 | PTB2     | ADC0_SE3, CMP0_IN3,<br>RF_NOT_ALLOWED,<br>DTM_TX, TPM1_CH0                      | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| D4 | РТВ3     | ADC0_SE2, CMP0_IN4,<br>CLKOUT, TPM1_CH1,<br>RTC_CLKOUT                          | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| D5 | NC       |                                                                                 |             | Not connected                                                     |

| D6 | NC       |                                                                                 |             | Not connected                                                     |

| D7 | GND      |                                                                                 | Ground      | Connect to ground                                                 |

| D8 | GND      |                                                                                 | Ground      | Connect to ground                                                 |

| D9 | ANT      |                                                                                 |             |                                                                   |

| E1 | PTC3     | TSI0_CH15, LLWU_P11,<br>RX_SWITCH, I2C1_SDA,<br>LPUART0_TX,<br>TPM0_CH1, DTM_TX | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| E2 | PTC2     | TSI0_CH14, LLWU_P10,<br>TX_SWITCH, I2C1_SCL,<br>LPUART0_RX,<br>CMT_IRO, DTM_RX  | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| E3 | NC       |                                                                                 |             | Not connected                                                     |

| E4 | NC       |                                                                                 |             | Not connected                                                     |

| E5 | PTC0     | LLWU_P9, I2C0_SCL,<br>LPUART0_CTS_b,<br>TPM0_CH1                                | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| No  | Pin Name              | Alternative Pin                                                                              | Pin Type    | Description                                                       |

|-----|-----------------------|----------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------|

| E6  | PTC6                  | TSI0_CH2, LLWU_P14,<br>XTAL_OUT_EN,<br>I2C1_SCL,<br>LPUART0_RX,<br>TPM2_CH0,<br>BSM_FRAME    | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| E7  | NC                    |                                                                                              |             | Not connected                                                     |

| E8  | GND                   |                                                                                              | Ground      | Connect to ground                                                 |

| E9  | GND                   |                                                                                              | Ground      | Connect to ground                                                 |

| F1  | GND                   |                                                                                              | Ground      | Connect to ground                                                 |

| F2  | NC                    |                                                                                              |             | Not connected                                                     |

| F3  | ADC0_DP0,<br>CMP0_IN0 |                                                                                              | Analog      |                                                                   |

| F4  | ADC0_DM0,<br>CMP0_IN1 |                                                                                              | Analog      |                                                                   |

| F5  | PTC4                  | TSI0_CH0, LLWU_P12,<br>LPUART0_CTS_b,<br>TPM1_CH0, BSM_DATA                                  | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| F6  | PTB18                 | DACO_OUT, ADCO_SE4,<br>CMPO_IN2, I2C1_SCL,<br>TPM_CLKIN0,<br>TPMO_CH0                        | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| F7  | PTC7                  | TSI0_CH3, LLWU_P15,<br>SPI0_PCS2, I2C1_SDA,<br>LPUART0_TX,<br>TPM2_CH1, BSM_DATA             | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| F8  | PTC5                  | TSI0_CH1, LLWU_P13,<br>RF_NOT_ALLOWED<br>LPTMR0_ALT2,<br>LPUART0_RTS_b,<br>TPM1_CH1, BSM_CLK | Digital I/O | Can be configured to use the mentioned alternative pin functions. |

| F9  | GND                   |                                                                                              | Ground      | Connect to ground                                                 |

| F11 | GND                   |                                                                                              | Ground      | Connect to ground                                                 |

| F12 | GND                   |                                                                                              | Ground      | Connect to ground                                                 |

#### **Transceiver Features** 2.3

The PAN4620 features an integrated chip antenna and corresponding matching networks. Both, a high accuracy 32 MHz crystal and a low frequency clock are integrated in the module. Therefore, no external crystal is required to make full use of the reduced power modes.

The operating frequency is in the ISM band and the MBAN band from 2360 MHz to 2483.5 MHz with a programmable output power from -30 dBm to 3 dBm

#### Bluetooth® Features 2.3.1

- Bluetooth® LE v4.2 (1 Mbps)

- Two simultaneous connections (2 independent hardware connection engines)

- Receive sensitivity of -93 dBm

For further information see ⇒ 4.9 Transceiver Feature Summary.

#### 2.3.2 IEEE<sup>®</sup> 802.15.4 Features

- IEEE® Standard 802.15.4-2011 compliant OQPSK modulation

- Receive sensitivity of -98 dBm (Receive sensitivity in generic FSK modes depends on mode selection and data rate.)

- Hardware acceleration for packet processing/link layer

- NXP®'s certified Thread® stack

For further information see ⇒ 4.9 Transceiver Feature Summary.

#### 2.3.3 **MCU Features**

The KW41Z features an ARM® Cortex-M0+MCU with up to 48 MHz. As compared to Cortex-M0, the Cortex-M0+ uses an optimized 2-stage pipeline microarchitecture for reduced power consumption and improved architectural performance (cycles per instruction).

#### 2.3.3.1 **Interrupt Controller**

- Supports up to 32 interrupt request sources

- 32 vectored interrupts, 4 programmable priority levels

- Includes a single non-maskable interrupt

- Supports interrupt handling when system clocking is disabled in low power modes

#### 2.3.3.2 On chip memory

- 512 kB flash memory implemented as two equal 256 kB blocks.

- One block can be read or erased, while code is being executed or read from the other.

- Flash can be marked execute only in 8 kB blocks to prevent code being from being read by third parties.

- 128 kB SRAM

- The chip features security circuitry to prevent unauthorized access to RAM and flash contents through the debugger.

#### 2.3.3.3 Debug Controller

- Serial wire debug (SWD) interface

- Hardware breakpoint unit for 2 code addresses

- Hardware watchpoint unit for 2 data items

- Micro trace buffer for program tracing

#### 2.3.4 Security Features

- Advanced encryption standard accelerator (AES-128 Accelerator)

- True random number generator (TRNG)

- Flash memory protection

#### 2.3.5 Power Management Control Unit

- Supports external voltage sources of 2.1 V to 4.2 V and is therefore ideally suited for single coin-cell battery operation.

- Programmable power saving modes

- Integrated low frequency clock to make full use of the reduced power modes

- Available wake-up from power saving modes via internal and external sources

- Integrated power-on reset (POR)

- Integrated low voltage detect (LVD) with reset (brownout) capability

- Selectable LVD trip points

- Programmable low voltage warning (LVW) interrupt capability

- Individual peripheral clocks can be gated off to reduce current consumption

- Internal buffered bandgap reference voltage

- Factory programmed trim for bandgap and LVD

- 1 kHz low power oscillator (LPO)

#### 2.3.6 Peripheral Features

- 16-bit analog-to-digital converter

- 12-Bit digital-to-analog converter

- High-speed analog comparator (CMP)

- Timer: low power timer (LPTMR), timer/PWM, programmable interrupt timer (PIT),

- Real-time clock (RTC)

- Inter-integrated circuit (I2C), two channels, up to 400 kHz, multi-master operation

- Low power universal asynchronous receiver transmitter (LPUART), one channel fullduplex operation

- Serial peripheral interface (SPI), master and slave mode, full-duplex, three-wire synchronous transfers

- Carrier modulator timer (CMT) with four modes of operation

- Touch sensor input with up to 16 external electrodes

- 24 General purpose Input/Outputs

- GPIOs can be configured to function as a interrupt driven keyboard scanning matrix

For further information see ⇒4.6 Interface Specification.

# 3 Detailed Description

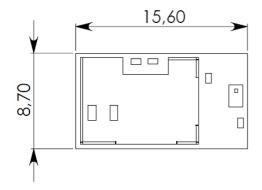

### 3.1 Dimensions

All dimensions are in millimeters.

| No. | Item   | Dimension | Tolerance | Remark    |

|-----|--------|-----------|-----------|-----------|

| 1   | Width  | 8.70      | ± 0.35    |           |

| 2   | Length | 15.60     | ± 0.35    |           |

| 3   | Height | 1.80      | ± 0.35    | With case |

### 3.2 Footprint

The outer dimensions have a tolerance of  $\pm 0.35$  mm.

#### Top view with all values in [mm]

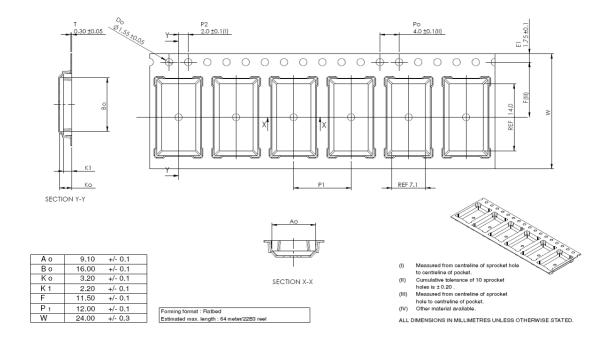

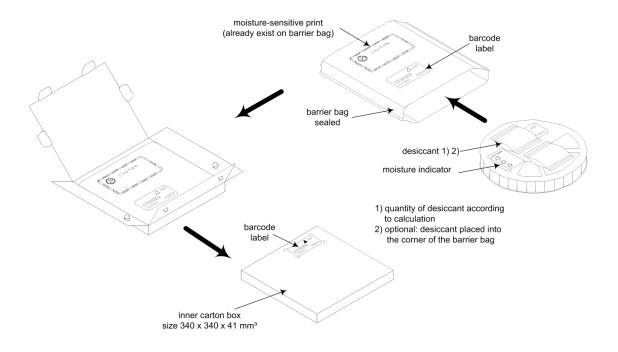

#### 3.3 Packaging

The product is an engineering sample status product and will be delivered in the package described below.

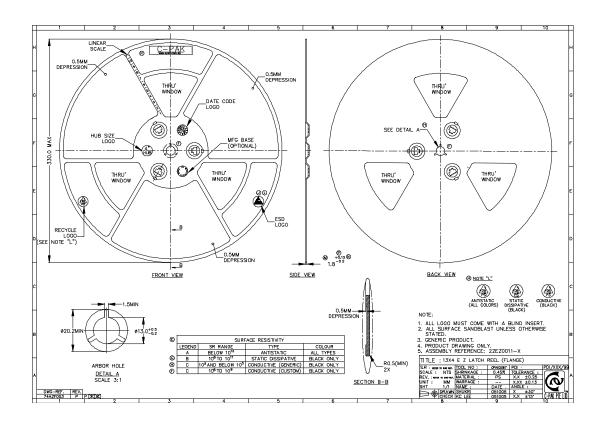

#### 3.3.1 Tape Dimensions

#### 3.3.2 Packing in Tape

Empty spaces in the component packed area shall be less than two per reel and those spaces shall not be consecutive.

The top cover tape shall not be found on reel holes and it shall not stick out from the reel.

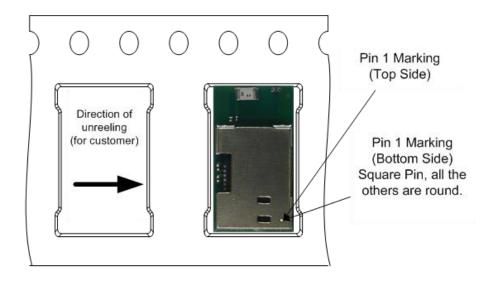

#### 3.3.3 Component Direction

100730-PAN1720.vsd

#### 3.3.4 Reel Dimension

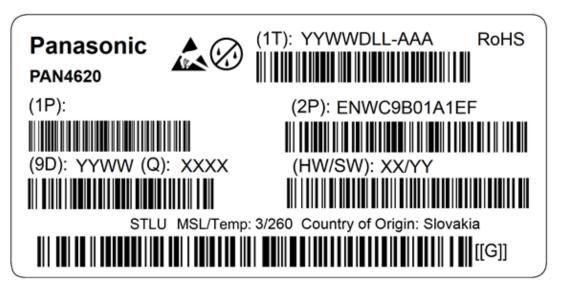

#### 3.3.5 Package Label

(1T) Lot code

(1P) Customer order number, if applicable

(2P) Order number

(9D) Date code

(Q) Quantity

(HW/SW) Hardware/software version

#### 3.3.6 Total Package

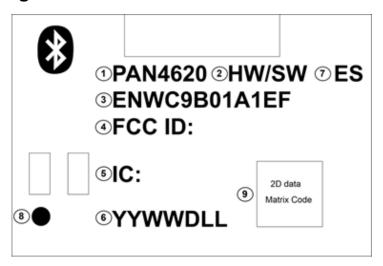

### 3.4 Case Marking

- 1 PAN4620

- 2 Hardware/Software Version

- 3 ENW-No. / Model Name

- 4 FCC ID

- 5 IC ID

- 6 Lot code

- 7 Engineering Sample marking, if applicable

- 8 Marking for Pin 1

- 9 2D barcode, for internal usage only

# 4 Specification

All specifications are over temperature and process, unless indicated otherwise.

#### 4.1 Default Test Conditions

Temperature:  $25 \pm 10 \,^{\circ}\text{C}$ Humidity:  $40 \text{ to } 85 \,^{\circ}\text{RH}$

Supply Voltage: 3.6 V

### 4.2 Absolute Maximum Ratings

The maximum ratings may not be exceeded under any circumstances, not even momentarily or individually, as permanent damage to the module may result.

| Symbol            | Parameter              | Condition                                             | Min.  | Тур. | Max.                 | Units |

|-------------------|------------------------|-------------------------------------------------------|-------|------|----------------------|-------|

| T <sub>STOR</sub> | Storage<br>Temperature |                                                       | -40   |      | +85                  | °C    |

| V <sub>ESD</sub>  | ESD robustness         | Electrostatic discharge voltage, human body model     | -2000 |      | +2000                | V     |

|                   |                        | Electrostatic discharge voltage, charged-device model | -500  |      | +500                 | V     |

| RF input power    | P <sub>max</sub>       |                                                       |       |      | 10                   | dBm   |

| $V_{DD}$          | Supply voltage         |                                                       | -0.3  |      | 4.2                  | V     |

| V <sub>IO</sub>   | Voltage on any IO pin  |                                                       | -0.3  |      | V <sub>DD</sub> +0.3 | V     |

### 4.3 Recommended Operating Conditions

The maximum ratings may not be exceeded under any circumstances, not even momentarily or individually, as permanent damage to the module may result.

| Symbol          | Parameter                  | Condition                                                                                                   | Min.                                     | Тур. | Max.                                     | Units |

|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------|------|------------------------------------------|-------|

| V <sub>DD</sub> | Supply voltage             | DCDC converter needs 2.1 V min to start, the supply can drop to min. of 1.8 V after DCDC converter settles. | Start up 2.1  Operating 1.8 <sup>1</sup> |      | 4.2                                      | V     |

| f <sub>IN</sub> | Input frequency            |                                                                                                             | 2.36                                     |      | 2.48                                     | GHz   |

| T <sub>A</sub>  | Ambient temperature range  |                                                                                                             | -40                                      | 25   | 85                                       | °C    |

| V <sub>IO</sub> | Voltage on any IO pin      |                                                                                                             | -0.3                                     |      | V <sub>DD</sub> +0.3                     | V     |

| I <sub>D</sub>  | Instantaneous max. current | Single pin limit (applies to all port pins)                                                                 | -25                                      |      | 25                                       | mA    |

| V <sub>IL</sub> | Logic low input voltage    |                                                                                                             | 0                                        |      | 0.3·<br>V <sub>DD INT</sub> <sup>2</sup> | V     |

| V <sub>IH</sub> | Logic high input voltage   |                                                                                                             | 0.7·V <sub>DD INT</sub>                  |      | V <sub>DD INT</sub>                      | V     |

\_

DC-DC converter requires slightly higher input voltage during startup. Bit DCDC\_STS\_DC\_OK will be set when the DC-DC converter finished the startup sequence. Typical startup time is 50 ms and it varies with the loading of the converter.

$<sup>^2</sup>$   $V_{\text{DD\,INT}}$  is the internal LDO regulated voltage supplying various circuit blocks,  $V_{\text{DD\,INT}}{=}1.2\,\text{V}.$

### 4.4 Current Consumption

The current consumption depends on the user scenario and on the setup and timing in the power modes.

Assume  $V_{DD} = 3.6 \text{ V}$ ,  $T_{amb} = 25 \,^{\circ}\text{C}$ , if nothing else is stated.

| Parameter                          | Condition                                                 | Min. | Тур. | Max. | Units |

|------------------------------------|-----------------------------------------------------------|------|------|------|-------|

| Typical average RX current         | Measured under continuous RX with MCU stop / Flash doze   |      | 8.4  |      | mA    |

| Typical average TX (0 dBm) current | Measured under continuous TX with MCU stop / Flash doze   |      | 7.6  |      | mA    |

| Typical average RX current         | Measured under continuous RX with MCU run / Flash enabled |      | 10.2 |      | mA    |

| Typical average TX (0 dBm) current | Measured under continuous TX with MCU run / Flash enabled |      | 9.6  |      | mA    |

| Low Power Mode current             | Current consumption in very low leakage stop mode         |      | 182  |      | nA    |

### 4.5 Internal Operating Frequencies

| Symbol             | Parameter                | Condition                       | Max. | Unit |

|--------------------|--------------------------|---------------------------------|------|------|

| f <sub>SYS</sub>   | System and core clock    | Normal run mode                 | 48   | MHz  |

| f <sub>BUS</sub>   | Bus clock                | Normal run mode                 | 24   | MHz  |

| f <sub>FLASH</sub> | Flash clock              | Normal run mode                 | 24   | MHz  |

| f <sub>LPTMR</sub> | LPTMR clock              | Normal run mode                 | 24   | MHz  |

| f <sub>SYS</sub>   | System and core clock    | VLPR and VLPS mode <sup>3</sup> | 4    | MHz  |

| f <sub>BUS</sub>   | Bus clock                | VLPR and VLPS mode <sup>3</sup> | 1    | MHz  |

| f <sub>FLASH</sub> | Flash clock              | VLPR and VLPS mode <sup>3</sup> | 1    | MHz  |

| f <sub>LPTMR</sub> | LPTMR clock <sup>4</sup> | VLPR and VLPS mode <sup>3</sup> | 24   | MHz  |

| f <sub>ERCLK</sub> | External reference clock | VLPR and VLPS mode <sup>3</sup> | 16   | MHz  |

<sup>&</sup>lt;sup>3</sup> The frequency limitations in VLPR and VLPS modes here override any frequency specification listed in the timing specification for any other module. These same frequency limits apply to VLPS, whether VLPS was entered from RUN or from VLPR.

\_

<sup>&</sup>lt;sup>4</sup> The LPTMR can be clocked at this speed in VLPR or VLPS only when the source is an external pin.

| Symbol                   | Parameter                      | Condition                       | Max. | Unit |

|--------------------------|--------------------------------|---------------------------------|------|------|

| f <sub>LPTMR-ERCLK</sub> | LPTMR external reference clock | VLPR and VLPS mode <sup>3</sup> | 16   | MHz  |

| f <sub>TPM</sub>         | TPM asynchronous clock         | VLPR and VLPS mode <sup>3</sup> | 8    | MHz  |

| f <sub>LPUART0</sub>     | LPUART0 asynchronous clock     | VLPR and VLPS mode <sup>3</sup> | 12   | MHz  |

## 4.6 Interface Specification

#### **4.6.1 LPUART**

See also Section ⇒ 4.8 General switching specification.

| Signal Name   | Description     | 1/0 | Pad        |

|---------------|-----------------|-----|------------|

| LPUART0_RX    | Receive Data    | 1   | B4, E2, E6 |

| LPUART0_TX    | Transmit Data   | I/O | A8, E1, F7 |

| LPUART0_CTS_b | Clear To Send   | I   | B3, E5, F5 |

| LPUART0_RTS_b | Request To Send | 0   | B5, C6, F8 |

| Description | Range                                           | Default.     |

|-------------|-------------------------------------------------|--------------|

| Baud rate   | Programmable baud rates (13-bit modulo divider) | 115200       |

| Data bits   | Programmable 8-bit or 9-bit data format         | 8 data bits  |

| Parity bits | Hardware parity generation and checking         | No parity    |

| Stop bit    | 1-2                                             | One stop bit |

## 4.6.2 Inter-Integrated Circuit (I<sup>2</sup>C)

Two  $I^2C$  channels. See also Section  $\Rightarrow$  4.8 General switching specification.

| Signal Name | Module | Description                        | 1/0 | Pad        |

|-------------|--------|------------------------------------|-----|------------|

| I2C0_SCL    | I2C0   | I <sup>2</sup> C serial clock line | I/O | B3, D1, E5 |

| I2C0_SDA    | I2C0   | I <sup>2</sup> C serial data line  | I/O | B5, C6, D2 |

| I2C1_SCL    | I2C1   | I <sup>2</sup> C serial clock line | I/O | B4, E2, E6 |

| I2C1_SDA    | I2C1   | I <sup>2</sup> C serial data line  | I/O | A8, E1, F7 |

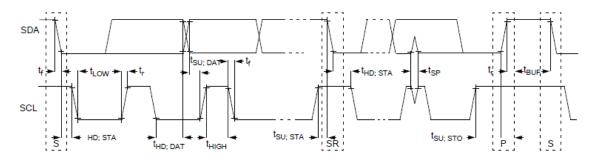

#### I<sup>2</sup>C timing (compare **Figure 1**):

| Symbol                | Description                                                                                  | Standard I       | Standard Mode     |                                    | Fast Mode |     |

|-----------------------|----------------------------------------------------------------------------------------------|------------------|-------------------|------------------------------------|-----------|-----|

|                       |                                                                                              | Min.             | Max.              | Min.                               | Max.      |     |

| f <sub>SCL</sub>      | SCL clock frequency                                                                          | 0                | 100               | 0                                  | 400       | kHz |

| t <sub>HD</sub> ; STA | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4                | -                 | 0.6                                | -         | μs  |

| t <sub>LOW</sub>      | LOW period of the SCL clock                                                                  | 4.7              | -                 | 1.3                                | -         | μs  |

| t <sub>HIGH</sub>     | HIGH period of the SCL clock                                                                 | 4                | -                 | 0.6                                | -         | μs  |

| t <sub>SU</sub> ; STA | Set-up time for a repeated START condition                                                   | 4.7              | -                 | 0.6                                | -         | μs  |

| t <sub>HD</sub> ; DAT | Data hold time for I <sup>2</sup> C bus devices                                              | 0 <sup>5</sup>   | 3.45 <sup>6</sup> | 07                                 | 0.96      | μs  |

| t <sub>SU</sub> ; DAT | Data set-up time                                                                             | 250 <sup>8</sup> | -                 | 100 <sup>6,9</sup>                 | -         | ns  |

| t <sub>r</sub>        | Rise time of SDA and SCL signals                                                             | -                | 1000              | 20+0.1C <sub>b</sub> <sup>10</sup> | 300       | ns  |

| t <sub>f</sub>        | Fall time of SDA and SCL signals                                                             | -                | 300               | 20+0.1C <sub>b</sub> <sup>9</sup>  | 300       | ns  |

| t <sub>SU</sub> ; STO | Set-up time for STOP condition                                                               | 4                | -                 | 0.6                                | -         | μs  |

| t <sub>BUF</sub>      | Bus free time between STOP and START condition                                               | 4.7              | -                 | 1.3                                | -         | μs  |

| t <sub>SP</sub>       | Width of spikes that must be suppressed by the input filter                                  | N/A              | N/A               | 0                                  | 50        | μs  |

<sup>&</sup>lt;sup>5</sup> The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL lines.

$<sup>^6</sup>$  The maximum  $t_{HD};$  DAT must be met only if the device does not stretch the LOW period ( $t_{LOW})$  of the SCL signal.

<sup>&</sup>lt;sup>7</sup> Input signal Slew = 10 ns and Output Load = 50 pF.

<sup>&</sup>lt;sup>8</sup> Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

$<sup>^9</sup>$  A Fast mode  $I^2$ C bus device can be used in a Standard mode  $I^2$ C bus system, but the requirement  $t_{SU}$ ; DAT  $\geq$  250 ns must then be met. This is automatically the case, if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal then it must output the next data bit to the SDA line  $t_{max} + t_{SU}$ ; DAT = 1000 + 250 = 1250 ns (according to the Standard mode  $I^2$ C bus specification), before the SCL line is released.

$<sup>^{10}</sup>$  C<sub>b</sub> = total capacitance of the one bus line in pF.

Figure 1 - Timing definition for fast and standard mode devices on the I<sup>2</sup>C bus.

#### 4.6.3 DMA Serial Peripheral Interface (DSPI)

Two independent SPI channels Master/Slave.

| Signal Name | Module | Description              | 1/0 | Pad |

|-------------|--------|--------------------------|-----|-----|

| SPI0_PCS0   | SPI0   | Chip Select/Slave Select | I/O | В3  |

| SPI0_PCS1   | SPI0   | Chip Select              | 0   | C4  |

| SPI0_PCS2   | SPI0   | Chip Select              | 0   | F7  |

| SPI0_SCK    | SPI0   | Serial Clock             | I/O | B5  |

| SPI0_SIN    | SPI0   | Data In                  | I   | A8  |

| SPI0_SOUT   | SPI0   | Data Out                 | 0   | B4  |

| SPI1_PCS0   | SPI1   | Chip Select/Slave Select | I/O | В3  |

| SPI1_SCK    | SPI1   | Serial Clock             | I/O | C3  |

| SPI1_SIN    | SPI1   | Data In                  | I   | B2  |

| SPI1_SOUT   | SPI1   | Data Out                 | 0   | B6  |

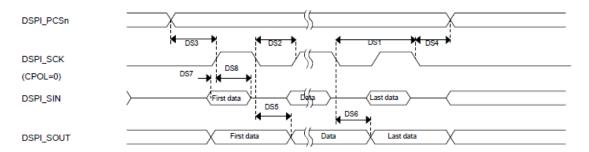

#### 4.6.3.1 DSPI switching specifications (limited voltage range)

Master mode DSPI timing (compare Figure 2):

Description **Symbol** Min. Max. Unit ٧ Operating voltage 2.7 3.6 Frequency of operation 12 MHz DS1 DSPI\_SCK output cycle time  $2 x t_{BUS}$ ns DS2 DSPI\_SCK output high/low time  $(t_{SCK}/2)-2$  $(t_{SCK}/2)+2$ ns DSPI\_PCSn valid to DSPI\_SCK delay<sup>11</sup> DS3  $(t_{BUS} \times 2)-2$ ns

\_

<sup>&</sup>lt;sup>11</sup> The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

| Symbol | Description                                       | Min.                     | Max. | Unit |

|--------|---------------------------------------------------|--------------------------|------|------|

| DS4    | DSPI_SCK to DSPI_PCSn invalid delay <sup>12</sup> | (t <sub>BUS</sub> x 2)-2 | -    | ns   |

| DS5    | DSPI_SCK to DSPI_SOUT valid                       | -                        | 8.5  | ns   |

| DS6    | DSPI_SCK to DSPI_SOUT invalid                     | -2                       | -    | ns   |

| DS7    | DSPI_SIN to DSPI_SCK input setup                  | 16.2                     | -    | ns   |

| DS8    | DSPI_SCK to DSPI_SIN input hold                   | 0                        | -    | ns   |

Figure 2 - Master mode DSPI timing.

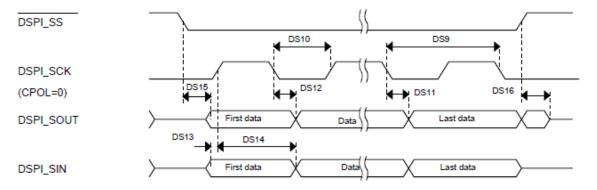

#### Slave mode DSPI timing (compare Figure 3):

| Symbol | Description                              | Min.                    | Max.                    | Unit |

|--------|------------------------------------------|-------------------------|-------------------------|------|

|        | Operating voltage                        | 2.7                     | 3.6                     | V    |

|        | Frequency of operation                   | -                       | 6                       | MHz  |

| DS9    | DSPI_SCK output cycle time               | 4 x t <sub>BUS</sub>    | -                       | ns   |

| DS10   | DSPI_SCK output high/low time            | (t <sub>SCK</sub> /2)-2 | (t <sub>SCK</sub> /2)+2 | ns   |

| DS11   | DSPI_SCK to DSPI_SOUT valid              | -                       | 21.4                    | ns   |

| DS12   | DSPI_SCK to DSPI_SOUT invalid            | 0                       | -                       | ns   |

| DS13   | DSPI_SIN to DSPI_SCK input setup         | 2.6                     | -                       | ns   |

| DS14   | DSPI_SCK to DSPI_SIN input hold          | 7.0                     | -                       | ns   |

| DS15   | DSPI_SS active to DSPI_SOUT driven       | -                       | 14                      | ns   |

| DS16   | DSPI_SS inactive to DSPI_SOUT not driven | -                       | 14                      | ns   |

\_

$<sup>^{\</sup>rm 12}$  The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

Figure 3 - Slave mode DSPI timing.

#### 4.6.3.2 **DSPI** switching specifications (full voltage range)

Master mode DSPI timing (compare Figure 4):

| Symbol | Description                                       | Min.                     | Max.                    | Unit |

|--------|---------------------------------------------------|--------------------------|-------------------------|------|

|        | Operating voltage <sup>13</sup>                   | 1.71                     | 3.6                     | V    |

|        | Frequency of operation                            | -                        | 12                      | MHz  |

| DS1    | DSPI_SCK output cycle time                        | 2 x t <sub>BUS</sub>     | -                       | ns   |

| DS2    | DSPI_SCK output high/low time                     | (t <sub>SCK</sub> /2)-4  | (t <sub>SCK</sub> /2)+4 | ns   |

| DS3    | DSPI_PCSn valid to DSPI_SCK delay <sup>14</sup>   | (t <sub>BUS</sub> x 2)-4 | -                       | ns   |

| DS4    | DSPI_SCK to DSPI_PCSn invalid delay <sup>15</sup> | (t <sub>BUS</sub> x 2)-4 | -                       | ns   |

| DS5    | DSPI_SCK to DSPI_SOUT valid                       | -                        | 10                      | ns   |

| DS6    | DSPI_SCK to DSPI_SOUT invalid                     | -1.2                     | -                       | ns   |

| DS7    | DSPI_SIN to DSPI_SCK input setup                  | 23.3                     | -                       | ns   |

| DS8    | DSPI_SCK to DSPI_SIN input hold                   | 0                        | -                       | ns   |

<sup>&</sup>lt;sup>13</sup> The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

<sup>&</sup>lt;sup>14</sup> The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

<sup>&</sup>lt;sup>15</sup> The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

DSPI\_PCSn DS3 M DS4 DSPI\_SCK DS8 (CPOL=0) Last data DSPI\_SIN First data First data Data Last data DSPI\_SOUT

Figure 4 - Master mode DSPI timing.

#### Slave mode DSPI timing (compare Figure 5):

| Symbol | Description                              | Min.                    | Max.                    | Unit |

|--------|------------------------------------------|-------------------------|-------------------------|------|

|        | Operating voltage                        | 1.71                    | 3.6                     | V    |

|        | Frequency of operation                   | -                       | 6                       | MHz  |

| DS9    | DSPI_SCK output cycle time               | 4 x t <sub>BUS</sub>    | -                       | ns   |

| DS10   | DSPI_SCK output high/low time            | (t <sub>SCK</sub> /2)-4 | (t <sub>SCK</sub> /2)+4 | ns   |

| DS11   | DSPI_SCK to DSPI_SOUT valid              | -                       | 29.1                    | ns   |

| DS12   | DSPI_SCK to DSPI_SOUT invalid            | 0                       | -                       | ns   |

| DS13   | DSPI_SIN to DSPI_SCK input setup         | 3.2                     | -                       | ns   |

| DS14   | DSPI_SCK to DSPI_SIN input hold          | 7.0                     | -                       | ns   |

| DS15   | DSPI_SS active to DSPI_SOUT driven       | -                       | 25                      | ns   |

| DS16   | DSPI_SS inactive to DSPI_SOUT not driven | -                       | 25                      | ns   |

Figure 5 - Slave mode DSPI timing.

### 4.6.4 Carrier Modulator Timer (CMT)

| Signal Name | Description                                   | I/O | Pad    |

|-------------|-----------------------------------------------|-----|--------|

| CMT_IRO     | Carrier Modulator Transmitter Infrared Output | 0   | D2, E2 |

### 4.6.5 Touch Sensing Input (TSI)

| Signal Name   | Description                         | 1/0 | Pad            |  |                |

|---------------|-------------------------------------|-----|----------------|--|----------------|

| TSI0_CH[15:0] | Touch sensing input capacitive pins | I/O | TSI0_CH0 → F5  |  |                |

|               |                                     |     | TSI0_CH1 → F8  |  |                |

|               |                                     |     | TSI0_CH2 → E6  |  |                |

|               |                                     |     | TSI0_CH3 → F7  |  |                |

|               |                                     |     | TSI0_CH4 → B5  |  |                |

|               |                                     |     | TSI0_CH5 → B4  |  |                |

|               |                                     |     | TSI0_CH6 → A8  |  |                |

|               |                                     |     | TSI0_CH7 → B3  |  |                |

|               |                                     |     | TSI0_CH8 → C4  |  |                |

|               |                                     |     | TSI0_CH9 → C5  |  |                |

|               |                                     |     | TSI0_CH10 → B6 |  |                |

|               |                                     |     | TSI0_CH11 → B2 |  |                |

|               |                                     |     |                |  | TSI0_CH12 → C3 |

|               |                                     |     | TSI0_CH13 → C2 |  |                |

|               |                                     |     | TSI0_CH14 → E2 |  |                |

|               |                                     |     | TSI0_CH15 → E1 |  |                |

#### TSI electrical specifications:

| Symbol   | Description                                                                        | Min. | Тур | Max. | Unit |

|----------|------------------------------------------------------------------------------------|------|-----|------|------|

| Ta       | Ambient temperature                                                                | -30  | -   | 85   | °C   |

| TSI_RUNF | Fixed power consumption in run mode                                                | -    | 100 | -    | μA   |

| TSI_RUNV | Variable power consumption in run mode (depends on oscillator's current selection) | 1.0  | -   | 128  | μΑ   |

| TSI_EN   | Power consumption in enable mode                                                   | -    | 100 | -    | μA   |

| TSI_DIS  | Power consumption in disable mode                                                  | -    | 1.2 | -    | μA   |

| TSI_TEN  | TSI analog enable time                                                             | -    | 66  | -    | μs   |

| Symbol    | Description                                        | Min. | Тур | Max. | Unit |

|-----------|----------------------------------------------------|------|-----|------|------|

| TSI_CREF  | TSI reference capacitor                            | -    | 1.0 | -    | pF   |

| TSI_DVOLT | Voltage variation of VP & VM around nominal values | 0.19 | -   | 1.03 | V    |

#### 4.6.6 General Purpose Input/Output (GPIO)

| Signal Name     | Description                  | I/O | Pad        |

|-----------------|------------------------------|-----|------------|

| PTA[19:16][2:0] | General Purpose Input/Output | I/O | PTA0 → C4  |

|                 |                              |     | PTA1 → C5  |

|                 |                              |     | PTA2 → A3  |

|                 |                              |     | PTA16 → B6 |

|                 |                              |     | PTA17 → B2 |

|                 |                              |     | PTA18 → C3 |

|                 |                              |     | PTA19 → C2 |

| PTB[18][3:0]    | General Purpose Input/Output | I/O | PTB0 → D1  |

|                 |                              |     | PTB1 → D2  |

|                 |                              |     | PTB2 → D3  |

|                 |                              |     | PTB3 → D4  |

|                 |                              |     | PTB18 → F3 |

| PTC[19:16][7:0] | General Purpose Input/Output | I/O | PTC0 → E5  |

|                 |                              |     | PTC1 → A8  |

|                 |                              |     | PTC2 → E2  |

|                 |                              |     | PTC3 → E1  |

|                 |                              |     | PTC4 → F5  |

|                 |                              |     | PTC5 → F8  |

|                 |                              |     | PTC6 → E6  |

|                 |                              |     | PTC7 → F7  |

|                 |                              |     | PTC16 → B5 |

|                 |                              |     | PTC17 → B4 |

|                 |                              |     | PTC18 → A8 |

|                 |                              |     | PTC19 → B3 |

The maximum input voltage on PTC0/1/2/3 is  $V_{DD}$ +0.3V.

### 4.6.7 Low-Leakage Wakeup (LLWU)

| Signal Name  | Description   | I/O | Pad           |

|--------------|---------------|-----|---------------|

| LLWU_P[15:0] | Wakeup inputs | I   | LLWU_P0 → B5  |

|              |               |     | LLWU_P1 → B4  |

|              |               |     | LLWU_P2 → A8  |

|              |               |     | LLWU_P3 → B3  |

|              |               |     | LLWU_P4 → B6  |

|              |               |     | LLWU_P5 → B2  |

|              |               |     | LLWU_P6 → C3  |

|              |               |     | LLWU_P7 → C2  |

|              |               |     | LLWU_P8 → D1  |

|              |               |     | LLWU_P9 → E5  |

|              |               |     | LLWU_P10 → E2 |

|              |               |     | LLWU_P11 → E1 |

|              |               |     | LLWU_P12 → F5 |

|              |               |     | LLWU_P13 → F8 |

|              |               |     | LLWU_P14 → E6 |

|              |               |     | LLWU_P15 → F7 |

### 4.6.8 Radio Module Signals

| Signal Name    | Description                                                                   | I/O | Pad        |

|----------------|-------------------------------------------------------------------------------|-----|------------|

| DTM_RX         | Direct test mode receive                                                      | I   | B4, D2, E2 |

| DTM_TX         | Direct test mode transmit                                                     | 0   | A8, D3, E1 |

| BSM_CLK        | Bit streaming mode (BSM) clock signal, 802.15.4 packet data stream clock line | 0   | B3, F8     |

| BSM_FRAME      | Bit streaming mode frame signal, 802.15.4 packet data stream frame line       | 0   | B4, E6     |

| BSM_DATA       | Bit streaming mode data signal, 802.15.4 packet data stream data line         | I/O | A8, F5, F7 |

| RF_RESET       | Radio reset signal                                                            | I   | B2         |

| BLE_RF_ACTIVE  | Signal to indicate future BLE activity.                                       | 0   | B3, C6     |

| RF_NOT_ALLOWED | Radio off signal, intended for Wi-Fi coexistence control                      | I   | D3, F8     |

| Signal Name | Description                           | I/O | Pad |

|-------------|---------------------------------------|-----|-----|

| RX_SWITCH   | Front end module receive mode signal  | 0   | E1  |

| TX_SWITCH   | Front end module transmit mode signal | 0   | E2  |

### 4.6.9 Analog-to-Digital Converter (ADC)

| Signal Name  | Description                               | I/O | Pad           |               |

|--------------|-------------------------------------------|-----|---------------|---------------|

| ADC0_DM0     | ADC channel 0 differential input negative | I   | F4            |               |

| ADC0_DP0     | ADC channel 0 differential input positive | I   | F3            |               |

| ADC0_SE[5:1] | ADC channel 0 single-ended input          | I   | ADC0_SE1 → D2 |               |

|              |                                           |     |               | ADC0_SE2 → D4 |

|              |                                           |     | ADC0_SE3 → D3 |               |

|              |                                           |     | ADC0_SE4 → F6 |               |

|              |                                           |     | ADC0_SE5 → C2 |               |

#### 16-bit ADC operating conditions:

| Symbol            | Description                                                                                | Min.              | Typ <sup>16</sup> | Max.                    | Unit     |

|-------------------|--------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------------|----------|

| $V_{DDA}$         | Supply voltage absolute                                                                    | 1.71              | -                 | 3.6                     | V        |

| V <sub>REFH</sub> | ADC reference voltage high, internally sourced and factory trimmed                         | -                 | 1.2               | -                       | V        |

| V <sub>REFL</sub> | ADC reference voltage low                                                                  | -                 | GND               | -                       |          |

| V <sub>ADIN</sub> | Input voltage: 16-bit differential mode All other modes                                    | V <sub>REFL</sub> | -                 | 31/32·V <sub>REFH</sub> | V<br>V   |

| C <sub>ADIN</sub> | Input capacitance: 16-bit mode 8-bit / 10-bit / 12-bit modes                               | -                 | 8                 | 10<br>5                 | pF<br>pF |

| R <sub>ADIN</sub> | Input series resistance                                                                    | -                 | 2                 | 5                       | kΩ       |

| R <sub>AS</sub>   | Analog source resistance<br>(external) 13-bit / 12-bit modes<br>$f_{ADCK} < 4  \text{MHz}$ | -                 | -                 | 5                       | kΩ       |

| f <sub>ADCK</sub> | ADC conversion clock frequency <sup>17</sup>                                               |                   |                   |                         |          |

$<sup>^{16}</sup>$  Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

-

| Symbol            | Description                     | Min.   | Typ <sup>16</sup> | Max.    | Unit |

|-------------------|---------------------------------|--------|-------------------|---------|------|

|                   | ≤ 13-bit mode                   | 1.0    | -                 | 18.0    | MHz  |

|                   | 16-bit mode                     | 2.0    | -                 | 12.0    | MHz  |

| C <sub>rate</sub> | ADC conversion rate:            |        |                   |         |      |

|                   | No ADC hardware averaging,      |        |                   |         |      |

|                   | continuous conversions enabled, |        |                   |         |      |

|                   | subsequent conversion time      |        |                   |         |      |

|                   | ≤ 13-bit modes                  | 20.000 | -                 | 818.330 | ksps |

|                   | 16-bit mode                     | 37.037 | -                 | 461.467 | ksps |

### 4.6.10 12-bit Digital-to-analog converter (DAC)

| Signal Name | Description | I/O | Pad |

|-------------|-------------|-----|-----|

| DAC0_OUT    | DAC output  | 0   | F6  |

#### 12-bit DAC operating requirements:

| Symbol            | Description                           | Min. | Max. | Unit |

|-------------------|---------------------------------------|------|------|------|

| $V_{DDA}$         | Supply voltage                        | 1.71 | 3.6  | V    |

| V <sub>DACR</sub> | Reference voltage <sup>18</sup>       | 1.2  | 3.6  | V    |

| C <sub>L</sub>    | Output load capacitance <sup>19</sup> | -    | 100  | pF   |

| IL                | Output load current                   | -    | 1    | mA   |

#### 12-bit DAC operating behaviors:

| Symbol                 | Description                                                               | Min. | Тур | Max. | Unit |

|------------------------|---------------------------------------------------------------------------|------|-----|------|------|

| I <sub>DDA_DACLP</sub> | Supply current - low-power mode                                           | -    | -   | 250  | μΑ   |

| I <sub>DDA_DACHP</sub> | Supply current – high speed mode                                          | -    | -   | 900  | μA   |

| t <sub>DACLP</sub>     | Full-scale settling time (0x080 to 0xF7F) - low-power mode <sup>20</sup>  | -    | 100 | 200  | μs   |

| t <sub>DACHP</sub>     | Full-scale settling time (0x080 to 0xF7F) - high-speed mode <sup>20</sup> | -    | 15  | 30   | μs   |

$<sup>^{\</sup>rm 17}$  To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

$<sup>^{18}</sup>$  The DAC reference can be selected to be  $V_{\text{DDA}}$  or  $V_{\text{REFH}}\text{=}1.2\,\text{V}.$

<sup>&</sup>lt;sup>19</sup> A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

<sup>&</sup>lt;sup>20</sup> Settling within ±1 LSB.

| Symbol               | Description                                                                                    | Min.                   | Тур          | Max.              | Unit       |

|----------------------|------------------------------------------------------------------------------------------------|------------------------|--------------|-------------------|------------|

| t <sub>CCDACLP</sub> | Code-to-code settling time (0xBF8 to 0xC08) - low-power mode and high-speed mode <sup>20</sup> | -                      | 0.7          | 1                 | μs         |

| V <sub>dacoutl</sub> | DAC output voltage range low - high-speed mode, no load, DAC set to 0x000                      | -                      | -            | 100               | mV         |

| V <sub>dacouth</sub> | DAC output voltage range high – high-speed mode, no load, DAC set to 0xFFF                     | V <sub>DACR</sub> -100 | -            | V <sub>DACR</sub> | mV         |

| INL                  | Integral non-linearity error – high-<br>speed mode <sup>21</sup>                               | -                      | -            | ±8                | LSB        |

| DNL                  | Differential non-linearity error - V <sub>DACR</sub> > 2 V <sup>22</sup>                       | -                      | -            | ±1                | LSB        |

| DNL                  | Differential non-linearity error - V <sub>DACR</sub> = VREF_OUT <sup>23</sup>                  | -                      | -            | ±1                | LSB        |

| V <sub>OFFSET</sub>  | Offset error <sup>24</sup>                                                                     | -                      | ±0.4         | ±0.8              | %FSR       |

| E <sub>G</sub>       | Gain error <sup>24</sup>                                                                       | -                      | ±0.1         | ±0.6              | %FSR       |

| PSRR                 | Power supply rejection ratio,<br>V <sub>DDA</sub> ≥ 2.4 V                                      | 60                     | -            | 90                | dB         |

| T <sub>CO</sub>      | Temperature coefficient offset voltage <sup>25</sup>                                           | -                      | 3.7          | -                 | μV/C       |

| $T_GE$               | Temperature coefficient gain error                                                             | -                      | 0.00042<br>1 | -                 | %FSR/<br>C |

| R <sub>OP</sub>      | Output resistance (load = 3 kΩ)                                                                | -                      | -            | 250               | Ω          |

| SR                   | Slew rate:                                                                                     |                        |              |                   |            |

|                      | High-power                                                                                     | 1.2                    | 1.7          | -                 | V/µs       |

|                      | Low-power                                                                                      | 0.05                   | 0.12         | -                 | V/µs       |

| BW                   | 3 dB bandwidth:                                                                                |                        |              |                   |            |

|                      | High-power                                                                                     | 550                    | -            | -                 | kHz        |

|                      | Low-power                                                                                      | 40                     | -            | -                 | kHz        |

$<sup>^{21}</sup>$  The INL is measured for 0 + 100 mV to  $V_{DACR}$  -100 mV.

$<sup>^{22}</sup>$  The DNL is measured for 0 + 100 mV to  $\ensuremath{V_{DACR}}$  –100 mV.

$<sup>^{23}</sup>$  The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V.

$<sup>^{24}</sup>$  Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  – 100 mV.

$<sup>^{25}</sup>$  V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high-power mode (DACx\_C0:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device.

# 4.6.11 Analog Comparator (CMP)

| Signal Name  | Description           | 1/0 | Pad           |

|--------------|-----------------------|-----|---------------|

| CMP0_IN[5:0] | Analog voltage inputs | I   | CMP0_IN0 → F3 |

|              |                       |     | CMP0_IN1 → F4 |

|              |                       |     | CMP0_IN2 → F6 |

|              |                       |     | CMP0_IN3 → D3 |

|              |                       |     | CMP0_IN4 → D4 |

|              |                       |     | CMP0_IN5 → D2 |

| CMP0_OUT     | Comparator output     | 0   | D1            |

#### CMP and 6-bit DAC electrical specifications:

| Symbol             | Description                                          | Min.                 | Тур | Max.     | Unit |

|--------------------|------------------------------------------------------|----------------------|-----|----------|------|

| $V_{DD}$           | Supply voltage                                       | 1.71                 | -   | 3.6      |      |

| I <sub>DDHS</sub>  | Supply current, high-speed mode (EN=1, PMODE=1)      | -                    | -   | 200      | μA   |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)       | -                    | -   | 20       | μA   |

| V <sub>AIN</sub>   | Analog input voltage                                 | V <sub>SS</sub> -0.3 | -   | $V_{DD}$ | V    |

| V <sub>AIO</sub>   | Analog input offset voltage                          | -                    | -   | 20       | mV   |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>26</sup>           |                      |     |          |      |

|                    | CR0[HYSTCTR] = 00                                    | -                    | 5   | -        | mV   |

|                    | CR0[HYSTCTR] = 01                                    | -                    | 10  | -        | mV   |

|                    | CR0[HYSTCTR] = 10                                    | -                    | 20  | -        | mV   |

|                    | CR0[HYSTCTR] = 11                                    | -                    | 30  | -        | mV   |

| V <sub>CMPOh</sub> | Output high                                          | V <sub>DD</sub> -0.5 | -   | -        | V    |

| V <sub>CMPOI</sub> | Output low                                           | -                    | -   | 0.5      | V    |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)   | 20                   | 50  | 200      | ns   |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)    | 80                   | 250 | 600      | ns   |

|                    | Analog comparator initialization delay <sup>27</sup> | -                    | -   | 40       | μs   |

$<sup>^{26}</sup>$  Typical hysteresis is measured with input voltage range limited to 0.6 to  $\rm V_{\rm DD}\!-\!0.6~\rm V.$

| Symbol             | Description                          | Min. | Тур | Max. | Unit              |

|--------------------|--------------------------------------|------|-----|------|-------------------|

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)    | -    | 7   | -    | μΑ                |

| INL                | 6-bit DAC integral non-linearity     | -0.5 | -   | 0.5  | LSB <sup>28</sup> |

| DNL                | 6-bit DAC differential non-linearity | -0.3 | -   | 0.3  | LSB               |

#### 4.6.12 Timer

| Signal Name     | Module     | Description             | I/O | Pad                   |

|-----------------|------------|-------------------------|-----|-----------------------|

| TPM_CLKIN[1:0]  | TPM0       | External clock          | I   | TPM_CLKIN0 → F6       |

|                 |            |                         |     | TPM_CLKIN1 → B2       |

| TPM0_CH[3:0]    | TPM0       | TPM channel             | I/O | TPM0_CH0 → F6, B6     |

|                 |            |                         |     | TPM0_CH1 → D1, E1     |

|                 |            |                         |     | TPM0_CH2 → C6, D2     |

|                 |            |                         |     | TPM0_CH3 → A3, B5     |

| TPM_CLKIN[1:0]  | TPM1       | External clock          | I   | TPM_CLKIN0 → F6       |

|                 |            |                         |     | TPM_CLKIN1 → B2       |

| TPM1_CH[1:0]    | TPM1       | TPM channel             | I/O | TPM1_CH0 → C4, C5, F5 |

|                 |            |                         |     | TPM1_CH1 → D3, D4, F8 |

| TPM_CLKIN[1:0]  | TPM2       | External clock          | I   | TPM_CLKIN0 → F6       |

|                 |            |                         |     | TPM_CLKIN1 → B2       |

| TPM2_CH[1:0]    | TPM2       | TPM channel             | I/O | TPM2_CH0 → C3, E6     |

|                 |            |                         |     | TPM2_CH1 → C2, F7     |

| LPTMR0_ALT[2:1] | LPTMR0     | Pulse counter input     | ı   | LPTMR0_ALT1 → D2      |

|                 |            | pin                     |     | LPTMR0_ALT2 → F8      |

| RTC_CLKOUT      | RTC Module | 1 Hz square-wave output | 0   | D4                    |

<sup>&</sup>lt;sup>27</sup> Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

$<sup>^{28}</sup>$  1 LSB =  $V_{reference}/64$

#### 4.6.13 Clocks

| Signal Name | Description                | 1/0 | Pad    |

|-------------|----------------------------|-----|--------|

| CLKOUT      | Internal clocks monitor    | 0   | D1, D4 |

| XTAL_OUT_EN | 32 MHz clock output enable | ı   | D1, E6 |

# 4.6.14 Serial Wire Debug (SWD)

| Signal Name | Description                         | Comment                           | I/O | Pad |

|-------------|-------------------------------------|-----------------------------------|-----|-----|

| SWD_DIO     | Serial wire debug data Input/Output | Pulled up internally by default   | I/O | C4  |

| SWD_CLK     | Serial wire clock                   | Pulled down internally by default | I   | C5  |

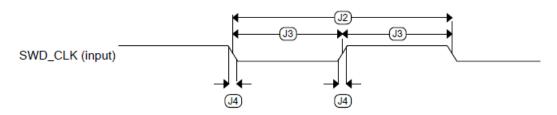

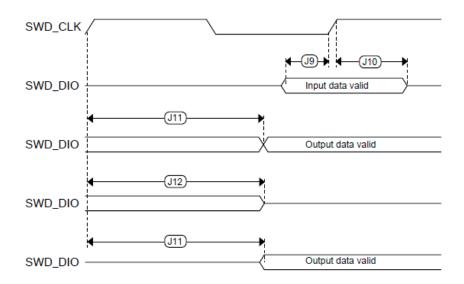

#### SWD full voltage range electricals as shown in Figure 6 and Figure 7:

| Symbol | Description                                     | Min. | Max. | Unit |

|--------|-------------------------------------------------|------|------|------|

|        | Operating voltage                               | 1.71 | 3.6  | V    |

| J1     | SWD_CLK frequency of operation                  | -    | 25   | MHz  |

| J2     | SWD_CLK cycle period                            | 1/J1 | -    | ns   |

| J3     | SWD_CLK clock pulse width                       | 20   | -    | ns   |

| J4     | SWD_CLK rise and fall times                     | -    | 3    | ns   |

| J9     | SWD_DIO input data setup time to SWD_CLK rise   | 10   | -    | ns   |

| J10    | SWD_DIO input data hold time after SWD_CLK rise | 0    | -    | ns   |

| J11    | SWD_CLK high to SWD_DIO data valid              | -    | 32   | ns   |

| J12    | SWD_CLK high to SWD_DIO high-Z                  | 5    | -    | ns   |

Figure 6 - SWD clock input timing.

Figure 7 - SWD data timing.