STRUCTURE: Silicon Monolithic integrated circuit

PRODUCT NAME: Servo signal processor for compact disc player

TYPE NAME: BU9543KV

FEATURES: The BU9543KV is a servo signal processor complete with built-in pre-servo amplifier and sampling

rate converter for application to compact disc player.

#### O Absolute maximum ratings (Ta=25°C)

| Items                         | Symbol            | Ratings    | Unit |

|-------------------------------|-------------------|------------|------|

| Power supply voltage          | V <sub>DD</sub>   | 4.5        | V    |

| Internal power supply voltage | V <sub>CORE</sub> | 2.5        | V    |

| Power dissipation             | P <sub>d</sub>    | 0.85 *1    | W    |

| Operating temp. range         | T <sub>opr</sub>  | -40 ~ +85  | °C   |

| Storage temp. range           | T <sub>stg</sub>  | -55 ~ +125 | °C   |

<sup>\*1</sup> Use of this processor at Ta = 25°C and over is subject to reduction of 8.5mW per 1°C.

#### O Recommendation Operating range (Ta=-40 ~ +85°C)

| Items                         | Symbol            | Ratings    | Unit |

|-------------------------------|-------------------|------------|------|

| Power supply voltage          | V <sub>DD</sub>   | 2.7 ~ 3.6  | V    |

| Internal power supply voltage | V <sub>CORE</sub> | 1.4 ~ 1.65 | V    |

<sup>\*</sup> This product is not designed for protection against radioactive rays.

#### O Electrical characteristics (Digital system)

$V_{DD}=3.0V$ ,  $V_{CORE}=1.5V$  (Unless otherwise specified Ta = 25°C)

|                                       | Items           |                 | Limit |     |      | Unit | Conditions             |

|---------------------------------------|-----------------|-----------------|-------|-----|------|------|------------------------|

|                                       |                 | Symbol          | MIN   | TYP | MAX  |      |                        |

| Input voltage                         | H-level voltage | V <sub>IH</sub> | 2.1   | -   | -    | V    |                        |

| input voitage                         | L-level voltage | V <sub>IL</sub> | -     | -   | 0.9  | V    |                        |

| Hysteresis                            | H-level voltage | V <sub>IH</sub> | 2.3   | -   | -    | V    |                        |

| input voltage                         | L-level voltage | V <sub>IL</sub> | -     | -   | 1.1  | V    |                        |

| Input L current to Pull-up resistor   |                 | I <sub>IL</sub> | -35   | -75 | -115 | μA   | V <sub>IN</sub> =0V    |

| Input H current to Pull-down resistor |                 | Lin             | 20    | 50  | 85   | μА   | V <sub>IN</sub> =3V    |

| Input current                         |                 | l <sub>i</sub>  | -     | -   | ±1   | μΑ   | V <sub>IN</sub> =0~3V  |

| Output                                | H-level voltage | V <sub>OH</sub> | 2.5   | -   | -    | V    | I <sub>0</sub> =-0.6mA |

| voltage                               | L-level voltage | V <sub>OL</sub> | -     | •   | 0.5  | V    | l <sub>0</sub> =0.6mA  |

#### Status of this document

The Japanese version of this document is the formal specification.

A customer may use this translation version only for a reference to help reading the formal version.

If there are any differences in translation version of this document, formal version takes priority.

The product described in this specification is designed to be used with ordinary electronic equipment or devices (such as audio-visual equipment, office-automation equipment, communications devices, electrical appliances, and electronic toys).

Should you intend to use this product with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

<sup>\*</sup> Operation is not guaranteed.

## O Electrical Characteristics (Analog system 1/2)

$V_{DD}$ =3.0V,  $V_{CORE}$ =1.5V (Unless otherwise specified Ta = 25°C,  $R_L$ =10k $\Omega$ , standard  $V_C$ )

| Itom                                 | Symbol             | Limit |      | Unit    | Applicable sine conditions |                                             |

|--------------------------------------|--------------------|-------|------|---------|----------------------------|---------------------------------------------|

| Item                                 | Symbol             | MIN   | TYP  | MAX     | Oill                       | Applicable pins, conditions                 |

| Total                                |                    |       |      |         |                            |                                             |

| Circuit current 1                    | l <sub>Q1</sub>    | •     | 10   | 27      | mA                         | AVDD1,AVDD2,DVDD                            |

| Circuit current 2                    | I <sub>Q2</sub>    | -     | 5    | 10      | mA                         | VDD_CORE                                    |

| PLL (VCO)                            |                    |       |      |         |                            |                                             |

| Max. oscillation<br>Frequency        | f <sub>VCOH</sub>  | 4.6   | 6.5  | -       | MHz                        | 1/4 of FLAG1 and VCO outputs                |

| Frequency Min. oscillation Frequency | fvcoL              | -     | 1.1  | 1.7     | MHz                        | 1/4 of FLAG1 and VCO outputs                |

| FC DAC                               |                    |       |      | <b></b> |                            | · · · · · · · · · · · · · · · · · · ·       |

| Offset voltage                       | V <sub>FCOF</sub>  | -50   | -    | 50      | mV                         | FCO                                         |

| Max. output voltage                  | V <sub>FCH</sub>   | 0.2   | 0.5  | -       | V                          | FCO                                         |

| Min. output voltage                  | V <sub>FCL</sub>   |       | -0.5 | -0.2    | V                          | FCO                                         |

| PCO                                  |                    |       |      | F       |                            |                                             |

| L-level output voltage               | V <sub>PCH</sub>   | -     | -1.0 | -0.6    | V                          | PCO                                         |

| H-level output voltage               | V <sub>PCL</sub>   | 0.6   | 1.0  | -       | V                          | PCO                                         |

| Audio DAC                            |                    |       |      |         |                            |                                             |

| Distortion rate                      | THD                | -     | 0.01 | -       | %                          | LDACO,RDACO,0dB 1kHz sine                   |

| Dynamic range                        | DR                 | -     | 90   | -       | dB                         | LDACO,RDACO,-60dB 1kHz sine                 |

| S/N ratio                            | S/N                | -     | 96   | -       | dB                         | LDACO,RDACO                                 |

| Max. output level                    | V <sub>SMAX</sub>  | 0.75  | 0.85 | 0.95    | $V_{rms}$                  | LDACO,RDACO,0dB 1kHz sine                   |

| EFM comparator                       |                    |       |      |         |                            |                                             |

| Threshold level                      | V <sub>EFM</sub>   | -200  | -    | 200     | mV                         | RFI,ANA_MONI0,FLAG2                         |

| Servo ADC                            |                    |       |      |         |                            |                                             |

| Offset voltage                       | V <sub>ADOF</sub>  | -140  | -    | 140     | mV                         | ANA_MONI0,ANA_MONI1                         |

| Max. conversion level                | . V <sub>ADH</sub> | 1.0   | 1.2  | 1.4     | V                          | ANA_MONI0,ANA_MONI1                         |

| Min. conversion level                | V <sub>ADL</sub>   | -1.4  | -1.2 | -1.0    | V                          | ANA_MONI0,ANA_MONI1                         |

| Servo DAC                            |                    |       |      |         |                            |                                             |

| Offset voltage                       | V <sub>DAOF</sub>  | -80   | -    | 80      | mV                         | FDOUT,TDOUT,SDOUT,CLVOUT                    |

| Max. output voltage                  | V <sub>DAH</sub>   | 0.8   | 1.2  | -       | ٧                          | FDOUT,TDOUT,SDOUT,CLVOUT                    |

| Min. output voltage                  | V <sub>DAL</sub>   | -     | -1.2 | -0.8    | V                          | FDOUT,TDOUT,SDOUT,CLVOUT                    |

| Bias amplifier                       |                    |       |      |         |                            |                                             |

| Max. output current                  | I <sub>BO</sub>    | •     | ±1.5 | -       | mA                         | VBIAS and BIAS fluctuation to be 200mV MAX. |

## O Electrical Characteristics (Analog system 2/2)

$V_{DD}$ =3.0V,  $V_{CORE}$ =1.5V (Unless otherwise specified Ta = 25°C,  $R_L$ =10k $\Omega$ , standard  $V_C$ )

| Item                   |                      | Limit |      | Unit | Applicable pine conditions |                                             |

|------------------------|----------------------|-------|------|------|----------------------------|---------------------------------------------|

| item                   | Symbol               | MIN   | TYP  | MAX  | Uiiii                      | Applicable pins, conditions                 |

| RF amplifier           |                      |       |      |      |                            |                                             |

| Offset voltage         | V <sub>RFOF</sub>    | -     | 0    | -    | mV                         | AC,BD,EQO                                   |

| Max. output voltage    | $V_{RFH}$            | 1.0   | 1.2  | -    | V                          | AC,BD,EQO                                   |

| Min. output voltage    | $V_{RFL}$            | -     | -1.3 | -1.1 | V                          | AC,BD,EQO                                   |

| FE amplifier           |                      |       |      |      |                            |                                             |

| Offset voltage         | V <sub>FEOF</sub>    | -     | 0    | -    | mV                         | AC,BD,ANA_MONI0,ANA_MONI1                   |

| Max. output voltage    | $V_{FEH}$            | 1.0   | 1.4  | -    | V                          | AC,BD,ANA_MONI0,ANA_MONI1                   |

| Min. output voltage    | V <sub>FEL</sub>     | -     | -1.4 | -1.0 | V                          | AC,BD,ANA_MONI0,ANA_MONI1                   |

| TE amplifier           |                      |       |      |      |                            |                                             |

| Offset voltage         | V <sub>TEOF</sub>    | -     | 70   | -    | mV                         | E,F,ANA_MONI0,ANA_MONI1                     |

| Max. output voltage    | V <sub>TEH</sub>     | 1.0   | 1.4  | -    | V                          | E,F,ANA_MONI0,ANA_MONI1                     |

| Min. output voltage    | V <sub>TEL</sub>     | -     | -1.4 | -1.0 | V                          | E,F,ANA_MONI0,ANA_MONI1                     |

| Asymmetric amplifier   | Asymmetric amplifier |       |      |      |                            |                                             |

| Offset voltage         | V <sub>ASYOF</sub>   | -     | 0    | -    | mV                         | ASY=V <sub>C</sub> ,RFI,ANA_MONI0(ASY_TEST) |

| Max. output voltage    | V <sub>ASYH</sub>    | 1.1   | 1.4  | -    | V                          | ASY,RFI,ANA_MONI0(ASY_TEST)                 |

| Min. output voltage    | V <sub>ASYL</sub>    | -     | -1.4 | -1.1 | V                          | ASY,RFI,ANA_MONI0(ASY_TEST)                 |

| APC                    |                      |       |      |      |                            |                                             |

| Output voltage1        | V <sub>APC1</sub>    | 2.4   | 2.8  | -    | V                          | PD="H",LD,ANA_MONI0(APCREF)                 |

| Output voltage2        | V <sub>APC2</sub>    | -     | 0.1  | 0.5  | V                          | PD="L",LD,ANA_MONI0(APCREF)                 |

| Max. reference voltage | V <sub>APCH</sub>    | -     | 220  | -    | mV                         | PD,LD,ANA_MONI0(APCREF)                     |

| Min. reference voltage | V <sub>APCL</sub>    | -     | 145  | -    | mV                         | PD,LD,ANA_MONI0(APCREF)                     |

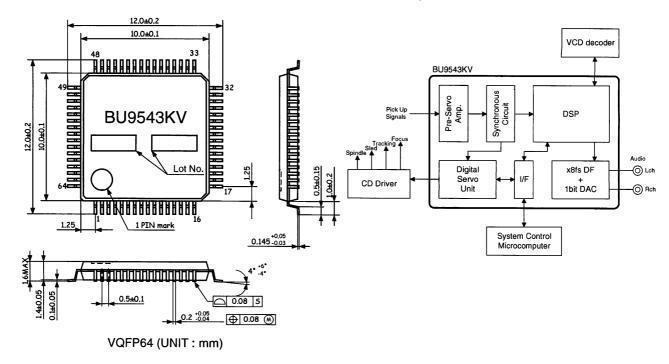

## O Package Outline, Appearance marking diagram

## O Block diagram

#### Description of Terminal

| No.       Name       Description of terminals         1       AVDD1       Analog power terminal         2       AC       A + C voltage input         3       BD       B + D voltage input         4       VBIAS       Bias level (VDD/2)         5       AGND1       Analog GND         6       E       E voltage input         7       F       F voltage input         8       PD       Photo detector input         9       LD       Laser drive output         10       ASY       For asymmetric correction         11       PCO       PCO output         12       FCO       FCO-DAC output         13       FDOUT       Focus drive output         14       TDOUT       Tracking drive output         15       SDOUT       Sled drive output         16       CLVOUT       CLV drive output         17       DVDD       Reference clock for SDRAM         18       MCK       Command transfer clock input         20       R/W       Command read/write signal         21       BUSY       Busy signal output         22       SUBSYQ       Sub code synchronous signal         23                            |     | Name -   |                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------------------------------|

| 2 AC A + C voltage input 3 BD B + D voltage input 4 VBIAS Bias level (VDD/2) 5 AGND1 Analog GND 6 E E voltage input 7 F F F voltage input 8 PD Photo detector input 9 LD Laser drive output 10 ASY For asymmetric correction 11 PCO PCO output 12 FCO FCO-DAC output 13 FDOUT Focus drive output 14 TDOUT Tracking drive output 15 SDOUT Sled drive output 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                | No. | Name     | Description of terminals     |

| 3       BD       B + D voltage input         4       VBIAS       Bias level (VDD/2)         5       AGND1       Analog GND         6       E       E voltage input         7       F       F voltage input         8       PD       Photo detector input         9       LD       Laser drive output         10       ASY       For asymmetric correction         11       PCO       PCO output         12       FCO       FCO-DAC output         13       FDOUT       Focus drive output         14       TDOUT       Tracking drive output         15       SDOUT       Sled drive output         16       CLVOUT       CLV drive output         17       DVDD       Reference clock for SDRAM         18       MCK       Command transfer clock input         19       DIN/DOUT       Command data input/output         20       R/W       Command read/write signal         21       BUSY       Busy signal output         22       SUBSYQ       Sub code synchronous signal         23       SUBDATA       Sub code bit clock input         24       SUBCK       Sub code bit clock input                    |     |          |                              |

| 4 VBIAS Bias level (VDD/2)  5 AGND1 Analog GND  6 E E voltage input  7 F F F voltage input  8 PD Photo detector input  9 LD Laser drive output  10 ASY For asymmetric correction  11 PCO PCO output  12 FCO FCO-DAC output  13 FDOUT Focus drive output  14 TDOUT Tracking drive output  15 SDOUT Sled drive output  16 CLVOUT CLV drive output  17 DVDD Reference clock for SDRAM  18 MCK Command transfer clock input  19 DIN/DOUT Command data input/output  20 R/W Command read/write signal  21 BUSY Busy signal output  22 SUBSYQ Sub code synchronous signal  23 SUBDATA Sub code data signal output  24 SUBCK Sub code bit clock input  25 WFCK Disc frame synchronous signal  26 VDD_CORE Internal digital power supply  27 DGND Digital GND  28 CLK Output for various clocks  29 CLK88 Clock output  31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                      |     |          |                              |

| 5 AGND1 Analog GND 6 E E voltage input 7 F F Voltage input 8 PD Photo detector input 9 LD Laser drive output 10 ASY For asymmetric correction 11 PCO PCO output 12 FCO FCO-DAC output 13 FDOUT Focus drive output 14 TDOUT Tracking drive output 15 SDOUT Sled drive output 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                             |     |          |                              |

| 6 E E voltage input 7 F F F voltage input 8 PD Photo detector input 9 LD Laser drive output 10 ASY For asymmetric correction 11 PCO PCO output 12 FCO FCO-DAC output 13 FDOUT Focus drive output 14 TDOUT Tracking drive output 15 SDOUT Sled drive output 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                              |     |          |                              |

| 7 F F Voltage input 8 PD Photo detector input 9 LD Laser drive output 10 ASY For asymmetric correction 11 PCO PCO output 12 FCO FCO-DAC output 13 FDOUT Focus drive output 14 TDOUT Tracking drive output 15 SDOUT Sled drive output 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                    |     |          |                              |

| 8 PD Photo detector input 9 LD Laser drive output 10 ASY For asymmetric correction 11 PCO PCO output 12 FCO FCO-DAC output 13 FDOUT Focus drive output 14 TDOUT Tracking drive output 15 SDOUT Sled drive output 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                        |     |          |                              |

| 9 LD Laser drive output  10 ASY For asymmetric correction  11 PCO PCO output  12 FCO FCO-DAC output  13 FDOUT Focus drive output  14 TDOUT Tracking drive output  15 SDOUT Sled drive output  16 CLVOUT CLV drive output  17 DVDD Reference clock for SDRAM  18 MCK Command transfer clock input  19 DIN/DOUT Command data input/output  20 R/W Command read/write signal  21 BUSY Busy signal output  22 SUBSYQ Sub code synchronous signal  23 SUBDATA Sub code data signal output  24 SUBCK Sub code bit clock input  25 WFCK Disc frame synchronous signal  26 VDD_CORE Internal digital power supply  27 DGND Digital GND  28 CLK Output for various clocks  29 CLK88 Clock output  31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                             | 7_  | •        |                              |

| 10 ASY For asymmetric correction 11 PCO PCO output 12 FCO FCO-DAC output 13 FDOUT Focus drive output 14 TDOUT Tracking drive output 15 SDOUT Sled drive output 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |          |                              |

| 11       PCO       PCO output         12       FCO       FCO-DAC output         13       FDOUT       Focus drive output         14       TDOUT       Tracking drive output         15       SDOUT       Sled drive output         16       CLVOUT       CLV drive output         17       DVDD       Reference clock for SDRAM         18       MCK       Command transfer clock input         19       DIN/DOUT       Command data input/output         20       R/W       Command read/write signal         21       BUSY       Busy signal output         22       SUBSYQ       Sub code synchronous signal         23       SUBDATA       Sub code data signal output         24       SUBCK       Sub code bit clock input         25       WFCK       Disc frame synchronous signal         26       VDD_CORE       Internal digital power supply         27       DGND       Digital GND         28       CLK       Output for various clocks         29       CLK88       Clock output for driver IC         30       RESETB       "L" → reset condition         31       XBUFO       X'tal buffer output | 9   | LD       |                              |

| 12 FCO FCO-DAC output 13 FDOUT Focus drive output 14 TDOUT Tracking drive output 15 SDOUT Sled drive output 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10  | ASY      | For asymmetric correction    |

| 13       FDOUT       Focus drive output         14       TDOUT       Tracking drive output         15       SDOUT       Sled drive output         16       CLVOUT       CLV drive output         17       DVDD       Reference clock for SDRAM         18       MCK       Command transfer clock input         19       DIN/DOUT       Command data input/output         20       R/W       Command read/write signal         21       BUSY       Busy signal output         22       SUBSYQ       Sub code synchronous signal         23       SUBDATA       Sub code bit clock input         24       SUBCK       Sub code bit clock input         25       WFCK       Disc frame synchronous signal         26       VDD_CORE       Internal digital power supply         27       DGND       Digital GND         28       CLK       Output for various clocks         29       CLK88       Clock output for driver IC         30       RESETB       "L" → reset condition         31       XBUFO       X'tal buffer output                                                                                    | 11  | PCO      | PCO output                   |

| 14 TDOUT Tracking drive output 15 SDOUT Sled drive output 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12  | FCO      | FCO-DAC output               |

| 15 SDOUT Sled drive output  16 CLVOUT CLV drive output  17 DVDD Reference clock for SDRAM  18 MCK Command transfer clock input  19 DIN/DOUT Command data input/output  20 R/W Command read/write signal  21 BUSY Busy signal output  22 SUBSYQ Sub code synchronous signal  23 SUBDATA Sub code data signal output  24 SUBCK Sub code bit clock input  25 WFCK Disc frame synchronous signal  26 VDD_CORE Internal digital power supply  27 DGND Digital GND  28 CLK Output for various clocks  29 CLK88 Clock output for driver IC  30 RESETB "L" → reset condition  31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13  | FDOUT    | Focus drive output           |

| 16 CLVOUT CLV drive output 17 DVDD Reference clock for SDRAM 18 MCK Command transfer clock input 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14  | TDOUT    | Tracking drive output        |

| 17 DVDD Reference clock for SDRAM  18 MCK Command transfer clock input  19 DIN/DOUT Command data input/output  20 R/W Command read/write signal  21 BUSY Busy signal output  22 SUBSYQ Sub code synchronous signal  23 SUBDATA Sub code data signal output  24 SUBCK Sub code bit clock input  25 WFCK Disc frame synchronous signal  26 VDD_CORE Internal digital power supply  27 DGND Digital GND  28 CLK Output for various clocks  29 CLK88 Clock output for driver IC  30 RESETB "L" → reset condition  31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15  | SDOUT    | Sled drive output            |

| 18       MCK       Command transfer clock input         19       DIN/DOUT       Command data input/output         20       R/W       Command read/write signal         21       BUSY       Busy signal output         22       SUBSYQ       Sub code synchronous signal         23       SUBDATA       Sub code data signal output         24       SUBCK       Sub code bit clock input         25       WFCK       Disc frame synchronous signal         26       VDD_CORE       Internal digital power supply         27       DGND       Digital GND         28       CLK       Output for various clocks         29       CLK88       Clock output for driver IC         30       RESETB       "L" → reset condition         31       XBUFO       X'tal buffer output                                                                                                                                                                                                                                                                                                                                        | 16  | CLVOUT   | CLV drive output             |

| 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17  | DVDD     | Reference clock for SDRAM    |

| 19 DIN/DOUT Command data input/output 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18  | MCK      | Command transfer clock input |

| 20 R/W Command read/write signal 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19  | DIN/DOUT |                              |

| 21 BUSY Busy signal output 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20  |          |                              |

| 22 SUBSYQ Sub code synchronous signal 23 SUBDATA Sub code data signal output 24 SUBCK Sub code bit clock input 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21  | BUSY     |                              |

| 23       SUBDATA       Sub code data signal output         24       SUBCK       Sub code bit clock input         25       WFCK       Disc frame synchronous signal         26       VDD_CORE       Internal digital power supply         27       DGND       Digital GND         28       CLK       Output for various clocks         29       CLK88       Clock output for driver IC         30       RESETB       "L" → reset condition         31       XBUFO       X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22  | SUBSYQ   |                              |

| 24       SUBCK       Sub code bit clock input         25       WFCK       Disc frame synchronous signal         26       VDD_CORE       Internal digital power supply         27       DGND       Digital GND         28       CLK       Output for various clocks         29       CLK88       Clock output for driver IC         30       RESETB       "L" → reset condition         31       XBUFO       X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23  | SUBDATA  |                              |

| 25 WFCK Disc frame synchronous signal 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24  | SUBCK    |                              |

| 26 VDD_CORE Internal digital power supply 27 DGND Digital GND 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | WFCK     |                              |

| 27     DGND     Digital GND       28     CLK     Output for various clocks       29     CLK88     Clock output for driver IC       30     RESETB     "L" → reset condition       31     XBUFO     X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | VDD CORE |                              |

| 28 CLK Output for various clocks 29 CLK88 Clock output for driver IC 30 RESETB "L" → reset condition 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |          |                              |

| 29     CLK88     Clock output for driver IC       30     RESETB     "L" → reset condition       31     XBUFO     X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |          |                              |

| 30       RESETB       "L" → reset condition         31       XBUFO       X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |          |                              |

| 31 XBUFO X'tal buffer output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |          |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |          |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |          |                              |

| No. | Name      | Description of terminals          |

|-----|-----------|-----------------------------------|

| 33  | DVDD      | I/O Digital power supply          |

| 34  | DOUTA     | Audio serial data output          |

| 35  | LRCK      | Audio LR signal output            |

| 36  | DCK       | Audio serial bit clock output     |

| 37  | VDD_CORE  | Internal digital power supply     |

| 38  | DFDIN     | Audio serial data input           |

| 39  | DFLRCK    | Audio LR signal input             |

| 40  | DFDCK     | Audio serial bit clock input      |

| 41  | DFSCKI    | Audio system clock input          |

| 42  | DGND      | Digital GND                       |

| 43  | FLAG0     | Various flag output               |

| 44  | FLAG1     | Various flag output               |

| 45  | FLAG2     | Various flag output               |

| 46  | FLAG3     | Various flag output               |

| 47  | DVDD      | I/O Digital power supply          |

| 48  | XI        | X'tal connecting (input) terminal |

| 49  | XO        | X'tal connecting terminal         |

| 50  | DGND      | Digital GND                       |

| 51  | TEST_IN   | Test signal input                 |

| 52  | TEST_OUT  | Test signal output                |

| 53  | DVDD2     | I/O Digital power supply          |

| 54  | AGND2     | Audio system analog GND           |

| 55  | LDACO     | Audio Lch output                  |

| 56  | VCDAC     | Audio reference voltage           |

| 57  | RDACO     | Audio Rch output                  |

| 58  | AVDD2     | Audio analog power supply         |

| 59  | AD_MONI0  | Monitor signal output             |

| 60  | AD_MONI1  | Monitor signal output             |

| 61  | ANA_MONIO | Analog monitor signal output      |

| 62  | ANA_MONI1 | Analog monitor signal output      |

| 63  | RFI       | RF data re-input terminal         |

| 64  | EQO       | After-RF-equalizer output         |

#### O Cautions

## (1) ABSOLUTE MAXIMUM RATINGS

Permanent device damage may occur and break mode (open or short) can not be specified if power supply, operating temperature, and those of ABSOLUTE MAXIMUM RATINGS are exceeded. If such a special condition is expected, components for safety such as fuse must be used.

#### (2) Power Supply

Power and Ground line must be designed as low impedance in the PCB. Print patterns if digital power supply and analog power supply must be separated even if these have same voltage level. Print patterns for ground must be designed as same as power supply. These considerations avoid analog circuits from the digital circuit noise. All pair of power supply and ground must have their own de-coupling capacitor. Those capacitor should be checked about their specification, etc. (nominal electrolytic capacitor degrades its capacity at low temperature) and choose the constant of an electrolytic capacitor.

(3) Functionality in the strong electro-magnetic field Malfunction may occur if in the strong electro-magnetic field.

#### (4) Input terminals

All LSI contain parasitic components. Some are junctions which normally reverse bias. When these junctions forward bias, currents flows on unwanted path, malfunction or device damage may occur. To prevent this, all input terminal voltage must be between ground and power supply, or in the range of guaranteed value in the Electrical characteristics. And no voltage should be supplied to all input terminal when power is not supplied.

#### Notes

- No technical content pages of this document may be reproduced in any form or transmitted by any

means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the

product described in this document are for reference only. Upon actual use, therefore, please request

that specifications to be separately delivered.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard

use and operation. Please pay careful attention to the peripheral conditions when designing circuits

and deciding upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or

otherwise dispose of the same, no express or implied right or license to practice or commercially

exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

#### About Export Control Order in Japan

Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan.

In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available,

please contact your nearest sales office.

### Please contact our sales offices for details;

```

U.S.A / San Diego

TEL: +1(858)625-3630

FAX: +1(858)625-3670

Atlanta

TEL: +1(770)754-5972

FAX: +1(770)754-0691

Dallas

TEL: +1(972)312-8818

FAX: +1(972)312-0330

Germany / Dusseldorf

TEL: +49(2154)9210

FAX: +49(2154)921400

United Kingdom / London TEL: +44(1)908-282-666

FAX: +44(1)908-282-528

France / Paris

TEL: +33(0)1 56 97 30 60 FAX: +33(0) 1 56 97 30 80

China / Hong Kong

TEL: +852(2)740-6262

FAX: +852(2)375-8971

Shanghai

TEL: +86(21)6279-2727

FAX: +86(21)6247-2066

Dilian

TEL: +86(411)8230-8549

FAX: +86(411)8230-8537

Beijing

TEL: +86(10)8525-2483

FAX: +86(10)8525-2489

Taiwan / Taipei

TEL: +866(2)2500-6956

FAX: +866(2)2503-2869

Korea / Seoul

TEL: +82(2)8182-700

FAX: +82(2)8182-715

Singapore

TEL: +65-6332-2322

FAX: +65-6332-5662

Malaysia / Kuala Lumpur

TEL: +60(3)7958-8355

FAX: +60(3)7958-8377

Philippines / Manila

TEL: +63(2)807-6872

FAX: +63(2)809-1422

Thailand / Bangkok

TEL: +66(2)254-4890

FAX: +66(2)256-6334

```

# Japan / (Internal Sales)

Tokyo 2-1-1, Yaesu, Chuo-ku, Tokyo 104-0082

TEL: +81(3)5203-0321 FAX: +81(3)5203-0300

Yokohama 2-4-8, Shin Yokohama, Kohoku-ku, Yokohama, Kanagawa 222-8575

TEL: +81(45)476-2131 FAX: +81(45)476-2128

Nagoya Dainagayo Building 9F 3-28-12, Meieki, Nakamura-ku, Nagoya, Aichi 450-0002

TEL: +81(52)581-8521 FAX: +81(52)561-2173

Kyoto 579-32 Higashi Shiokouji-cho, Karasuma Nishi-iru, Shiokoujidori, Shimogyo-ku,

Kyoto 600-8216

TEL: +81(75)311-2121 FAX: +81(75)314-6559

(Contact address for overseas customers in Japan)

Yokohama TEL: +81(45)476-9270 FAX: +81(045)476-9271